Wprowadzenie do problemu / definicja luki

Ministerstwo Gospodarki, Handlu i Przemysłu Japonii (METI) opublikowało kompletne „OT Security Guidelines for Semiconductor Device Factories” — pierwszy tak kompleksowy zbiór dobrych praktyk OT zaprojektowany pod specyfikę fabów półprzewodników. Dokument (ok. 130 stron) dostępny jest po japońsku i po angielsku i opisuje architekturę referencyjną, klasy zagrożeń oraz wymagalne środki ochrony i operacji bezpieczeństwa (w tym FSIRT) dla środowisk cleanroom i zaplecza IT/OT.

W skrócie

- Zakres: pełny cykl bezpieczeństwa OT w fabach chipów — od inwentaryzacji narzędzi procesowych, przez segmentację i hardening, po monitorowanie i odtwarzanie.

- Cel: utrzymanie ciągłości produkcji i jakości wyrobów, ochrona tajemnic produkcyjnych oraz ograniczanie wpływu incydentów na łańcuch dostaw.

- Poziom przeciwnika: wytyczne formalnie zakładają gotowość na APT na poziomie SL4 (IEC 62443).

- Status: finalne wytyczne opublikowane 24 października 2025 r., po wcześniejszej konsultacji publicznej z czerwca 2025 r.

Kontekst / historia / powiązania

W ostatnich latach sektor półprzewodników stał się krytyczny gospodarczo i geopolitycznie; każde zakłócenie produkcji ma efekt domina w wielu branżach. Już w czerwcu 2025 r. METI pokazało wersję roboczą wytycznych i otworzyło konsultacje, które zakończyły się publikacją wersji 1.0 w październiku 2025 r. Wytyczne uzupełniają istniejące ramy (IEC 62443, NIST SP 800-82) oraz praktyki IPA (Information-technology Promotion Agency) w zakresie analizy ryzyka ICS.

Analiza techniczna / szczegóły wytycznych

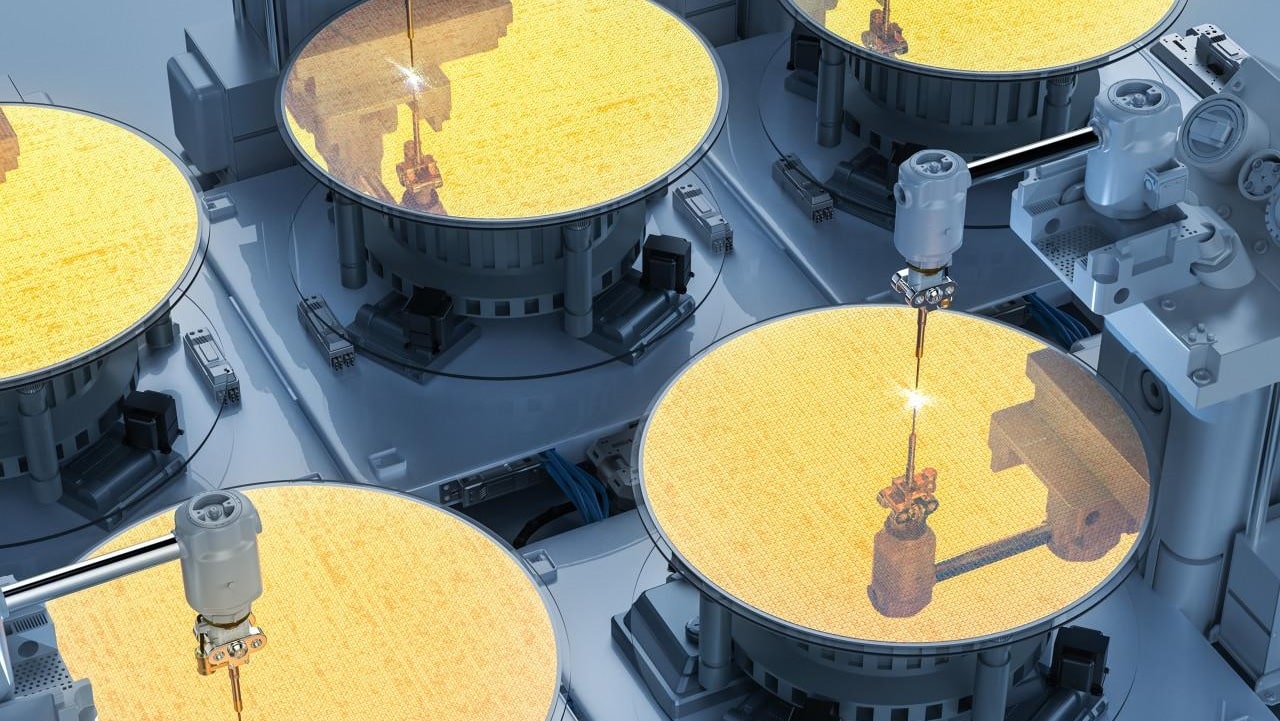

Architektura referencyjna fabu półprzewodników

Dokument przedstawia architekturę warstwową dla stref fabu (fab area) i zaplecza, w tym sieci dla narzędzi procesowych (tool networks), systemów MES/AMHS, serwerów retikli/parametrów procesu oraz interfejsów do IT/ERP. Zawiera mapowanie przepływów (EAP/GEM, SECS/GEM, OPC UA), kontrolę interfejsów i zasady komunikacji między strefami.

Zarządzanie zasobami i podatnościami (fab area)

- Obowiązkowa pełna inwentaryzacja tysięcy narzędzi (często >2000 urządzeń na fab) wraz z ich wersjami oprogramowania/firmware, interfejsami i zależnościami.

- Ocena podatności i priorytetyzacja na podstawie wpływu na cele produkcyjne/bezpieczeństwo jakości.

- Dodatkowe warstwy obrony (allow-listy, jump-hosty serwisowe, „golden image” do szybkiego odtworzenia).

Operacje bezpieczeństwa i FSIRT

Wytyczne wymagają zaprojektowania i utrzymania FSIRT (Factory Security Incident Response Team) odpowiedzialnego za monitorowanie, reagowanie, odtwarzanie oraz ciągłe doskonalenie w cyklu PDCA. Zakres obejmuje integrację OT SOC, playbooki forensyczno-produkcyjne i ćwiczenia z udziałem dostawców tooli.

Segmentacja, kontrola dostępu i fizyczne bezpieczeństwo

- Granularna segmentacja sieci (strefy/konduity), izolacja fab area od IT, kontrola ruchu M2M, DMZ dla serwisu zewnętrznego.

- Ścisła kontrola fizyczna: wejścia do cleanroom, polityka wnoszenia i podłączania mediów, kontrola portów serwisowych.

Odwołania do standardów

Dokument mapuje się do IEC 62443 i praktyk NIST SP 800-82, a w procesie analizy ryzyka wskazuje przewodniki IPA dla systemów sterowania.

Praktyczne konsekwencje / ryzyko

- Ryzyko przestojów i scrapu: zainfekowane lub błędnie skonfigurowane narzędzia (np. litho/etch/metrology) mogą degradować jakościowo całe partie wafli — wytyczne kładą nacisk na szybkie odtwarzanie i „blast radius reduction”.

- Łańcuch dostaw: wymagania wobec integratorów i serwisantów (zdalny dostęp, media wymienne, aktualizacje) zmieniają umowy i procesy audytowe.

- Zagrożenia APT: przyjęcie poziomu SL4 oznacza planowanie pod ataki z użyciem 0-day, living-off-the-land i podszywania się pod ruch serwisowy.

Rekomendacje operacyjne / co zrobić teraz

- Zrób gap-assessment względem wytycznych METI i IEC 62443: zacznij od inwentaryzacji tooli, krytyczności operacyjnej i mapy przepływów danych (SECS/GEM, OPC UA).

- Utwórz lub wzmocnij FSIRT dla fabu: role, on-call, playbooki odcięcia serwisu i „golden restore” tooli; przetestuj RTO/RPO na linii pilotażowej.

- Segmentacja i dostępy serwisowe: wprowadź dedykowane jump-hosty z nagrywaniem sesji, konta jednorazowe, MFA i allow-listy protokołów.

- Zarządzanie podatnościami w cleanroom: cykle patch/mitigation akceptowalne procesowo, kompensacje (application allowlisting, network isolation) dla „no-patch tools”.

- Fizyczne kontrole w fab area: e-ink dla zezwoleń, plombowanie portów, skanowanie nośników, „sterile media” i procedury wnoszenia narzędzi.

- Mapowanie do NIST SP 800-82 i praktyk IPA: wykorzystaj check-listy ICS i ich metody analizy ryzyka jako uzupełnienie lokalnych procedur.

Różnice / porównania z innymi przypadkami

- Wobec ogólnych przewodników ICS (NIST SP 800-82): METI idzie głębiej w specyfikę fabów półprzewodników (np. integracja AMHS/MES, interfejsy EAP/GEM, praktyki serwisu tooli), które w NIST są omawiane bardziej ogólnie.

- Wobec IEC 62443: japońskie wytyczne ustawiają docelowy poziom odporności (SL4) i proponują konkretne wzorce architektury i operacji, ułatwiające praktyczną implementację w fabie.

Podsumowanie / najważniejsze wnioski

- Japonia dostarczyła praktyczny, branżowy standard OT dla fabów chipów — spójny z IEC 62443 i NIST, a jednocześnie operacyjnie „przyziemiony”.

- Organizacje z łańcucha dostaw półprzewodników mogą użyć dokumentu METI jako wymagania bazowego dla dostawców i serwisantów.

- Największy nacisk położono na inwentaryzację tooli, segmentację, kontrolę serwisu oraz gotowość FSIRT — czyli obszary, które realnie skracają MTTR i ograniczają straty produkcyjne.

Źródła / bibliografia

- METI – OT Security Guidelines for Semiconductor Device Factories (v1.0, 24.10.2025, EN) – PDF. (meti.go.jp)

- METI – OTセキュリティガイドライン(半導体デバイス工場向け) – wersja japońska, PDF. (meti.go.jp)

- METI – (Draft) OT Security Guidelines… – ogłoszenie konsultacji (27.06.2025). (meti.go.jp)

- METI – Summary of (Draft) Guidelines – założenia SL4/IEC 62443 – PDF. (meti.go.jp)

- SecurityWeek – Japan Issues OT Security Guidance for Semiconductor Factories (31.10.2025). (SecurityWeek)