Wiecie, jak sprawdzić, czy w procesorze nie ukryto konia trojańskiego lub tylnej furtki? Weryfikacja tej hipotezy nie jest prostym zadaniem – nie jest to jednak niemożliwe. Poniżej znajdziecie przegląd metod używanych w takich sytuacjach przez ekspertów.

Błędy i podatności sprzętowe, o istnieniu których do tej pory tylko spekulowano, zaczęły znajdować potwierdzenie w wynikach testów i badań, np. Meltdown, rodzina Spectre, tzw. “afera Bloomberga”, a także problemy chińskich firm Huawei i ZTE. W rezultacie coraz częściej zadawane są pytania: Czy mój sprzęt (router/komórka/płyta) ma trojana? W jaki sposób mogę to sprawdzić? Jedną z metod wykrywania jest opisywany niedawno „fuzzing” procesorów, jednak nie wyczerpuje to zakresu dostępnych narzędzi. W tym artykule przedstawię przegląd sposobów detekcji zagrożeń sprzętowych w gotowych produktach, czyli tzw. metod post-produkcyjnych. Zakładamy zatem scenariusz, w którym dostajemy/kupujemy gotowy produkt bez możliwości wpłynięcia na jego proces produkcyjny i chcemy sprawdzić, czy to, co zawiera dokumentacja układu, pokrywa się ze stanem faktycznym.

Metody destrukcyjne, czyli krzemowy “rewers”

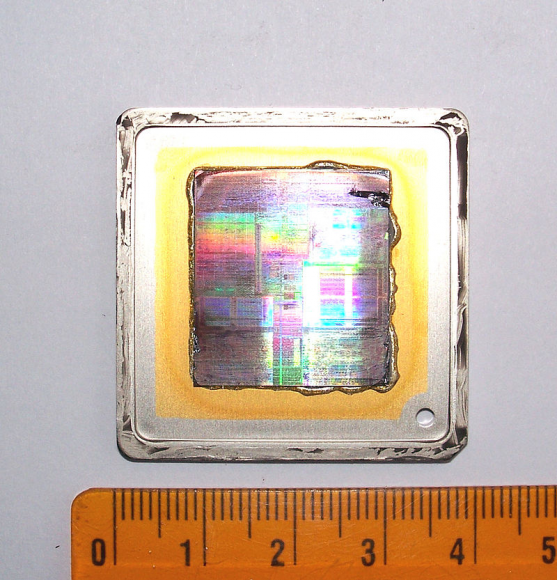

Intuicyjnie wykrywanie zagrożeń sprzętowych kojarzy się nam z inżynierią wsteczną układu scalonego. Jej celem jest zebranie jak największej ilości informacji na temat wewnętrznej struktury chipa w celu ustalenia założeń projektowych i zasad działania produktu. Odbywa się to poprzez uzyskanie fizycznego dostępu do elementu krzemowego (tzw. “kości”, ang. die) i jego analizie, patrz Rysunek 1 – najpierw dzięki metod optycznych a potem ewentualnie odczytu sygnałów bezpośrednio z powierzchni układu (jeśli to tylko możliwe, co dotyczy głównie starych bądź prostych układów). Już na wstępie warto jednak zaznaczyć, iż jest to rozwiązanie o bardzo wysokim poziomie skomplikowania (a więc drogie i czasochłonne), które wymaga tak sprzętu, jak i wysokich umiejętności.

Rysunek 1. Kość układu Intel Xeon E7440 o wymiarach 22×23 mm (506 mm2) zawierająca 19000000000000 tranzystorów, źródło Wikipedia.

Tak jak w przypadku rewersu oprogramowania, proces inżynierii wstecznej układu scalonego poprzedzony jest fazą przygotowawczą, podczas której zbierane są informacje o analizowanym produkcie, np. oficjalna dokumentacja techniczna, dane producenta o technologii wykonania w tym o konkretnym procesie litograficznym. Na tej podstawie należy dobrać narzędzia, które będą potrzebne w następujących po sobie fazach adekwatnych rewersu.

Rysunek 2. Etapy chemicznej dekapsulacji chipu z prezentacji M. Janke i P. Laackmanna, źródło.

Warto zauważyć, iż narzędzia do rewersu i analizy systemu są stosunkowo łatwo dostępne, a niezbędne prace można przeprowadzić na zwykłej stacji roboczej. zwykle wymaga disassemblera wspieranego przez narzędzia do wstecznej analizy kodu, np. IDAPro czy radare. W przypadku chipów krzemowych jest to proces zdecydowanie bardziej skomplikowany i wielostopniowy, patrz Rysunek 2.

Fazy analizy układu scalonego:

1) Dekapsulacja (ang. decapsulation), zwana również potocznie “skalpowaniem”, ma na celu usunięcie obudowy układu. W przypadku większych układów można z powodzeniem stosować metody mechaniczne. Jednak w przypadku małych scalaków w obudowach plastikowych (epoksydowych) czy porcelanowych (w tzw. „porcelanie”), przygotowanych np. do zastosowań wbudowanych (ang. embedded), sprawa jest trudniejsza. Proste metody mechaniczne, np. szlifowanie, mogą uszkodzić chip. choćby mała rysa może zdecydowanie utrudnić bądź wręcz uniemożliwić analizę wsteczną, a w najgorszym wypadku doprowadzi do błędnych rezultatów (np. zostanie zinterpretowana jako połączenie). W profesjonalnych laboratoriach stosuje się zatem silnie żrące kwasy rozpuszczające wszystko oprócz krzemu. Ich użycie wymaga jednak odpowiedniej infrastruktury, np. odpowiednich nawiewów, narzędzi (pipety, odczynniki), a co ważniejsze odpowiednio przeszkolonego i doświadczonego personelu.

2) Rozwarstwianie (ang. delayering). Układy scalone składają się z wielu nakładających się na siebie warstw zdefiniowanych przez konkretny proces fotolitograficzny, np. miejsca, w których różne domieszki są rozproszone w podłożu (warstwy dyfuzyjne), inne warstwy określają miejsca dodania (tzw. “wszczepienie”, ang. implant) dodatkowych jonów (warstwy implantu), jeszcze inne definiują przewodniki (domieszkowane warstwy polikrzemowe lub metalowe), a także definiują połączenia pomiędzy warstwami przewodzącymi (warstwy kontaktowe). W procesie inżynierii wstecznej wszystkie te warstwy układu scalonego są analizowane, a następnie usuwane po kolei przy użyciu metod chemicznych. Za każdym razem po usunięciu warstwy stosuje się polerowanie powierzchni, tzw. niwelowanie, aby utrzymać ją w konkretnej, zadanej płaszczyźnie.

3) Obrazowanie (ang. imagining). Każda warstwa układu jest dokładnie fotografowana, a następnie zdjęcia są łączone, by stworzyć pełny obraz. zwykle stosuje się do tego dedykowane oprogramowanie. Warto zauważyć, iż typowy układ scalony do zastosowań wbudowanych jest wykonany w procesie (technologii litograficznej) o rozdzielczości pomiędzy 0.18μm = 180nm (np. proste układy FPGA) i 45nm. Zwykły mikroskop optyczny (tzw. scanning optical microscope, SOM) jest zatem niewystarczający – uzyskuje w najlepszym wypadku rozdzielczość od 380nm do 200nm. Dlatego stosuje się rozwiązania alternatywne, np. mikroskopy elektronowe, które monitorują elektrony odbite od powierzchni krzemu, co pozwala na poprawę rozdzielczości do 5nm. Oczywiście mikroskopy elektronowe są droższe od „klasycznych”. Inną metodą poprawy rozdzielczości jest obserwacja zmian napięcia wywołanych światłem lasera podczas pracy układu (ang. light-induced voltage alteration, LIVA).

4) Opisanie (ang. annotation). Uzyskane obrazy są analizowane w celu identyfikacji podstawowych struktur elektronicznych (bramki, połączenia etc.), które są opisywane manualnie lub dzięki dedykowanego systemu do rozpoznawania konkretnych elementów na zdjęciach chipu. Podstawowa trudność w opisaniu zdjęć układu wynika z konieczności rekonstrukcji elementów trójwymiarowych na podstawie danych zbieranych oddzielnie dla każdej warstwy.

5) Odtworzenie schematu układu – ustalenie zasad pracy układu, np. pozyskanie hierarchicznej bądź tzw. płaskiej netlisty, na podstawie obrazów z przypisami, jak również informacji udostępnionych przez producenta (dokumentacja techniczna, datasheety itp.).

Krzemowy rewers jest zatem bardzo skomplikowany, wymaga ogromnej precyzji, a ponadto obciążony jest wadami. Pierwsza i najpoważniejsza wada wynika z faktu, iż niszczymy układ poddany obserwacji. Dlatego w literaturze rewers zaliczany jest do metod “destrukcyjnych” (ang. destructive methods). Pierwsze trzy z opisanych faz rewersu wyodrębniają struktury elektroniczne w układzie scalonym. Pomijając możliwość uszkodzenia układu podczas procesu dekapsulacji, fizyczne usuwanie i niwelowanie warstw (wymagane przy analizie większości produktów) wpływa negatywnie na struktury w odsłoniętych i znajdujących się poniżej warstwach, np. powstają dodatkowe połączenia. Może prowadzić to do błędnych wyników, dlatego rewers powinno się przeprowadzać na kilku układach równolegle.

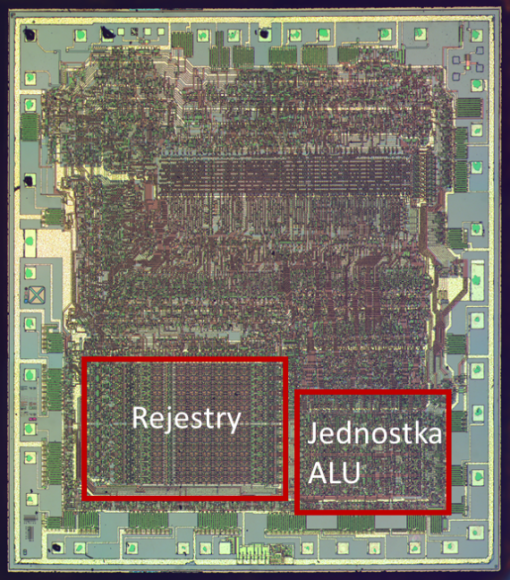

Rysunek 3. Zdjęcie struktury układu Z80, źródło: Wikipedia, oznaczenia autora.

Jednak i ostatnie dwa kroki (opisanie i odtworzenie) stanowią spore wyzwanie, wymagając pracy bardzo doświadczonych analityków. Dlaczego? Na końcowy kształt układu elektronicznego mają często wpływ czynniki niemające nic wspólnego z techniką. Analityk dokonujący rewersu układu scalonego powinien uwzględnić stan wiedzy, rozwiązania techniczne, jak również sytuację ekonomiczną czy konkretne cele projektowe, które mogły wpłynąć na wdrożenie badanego układu. Dobrym przykładem są procesory z lat 70. i 80., które ze względu na wykonanie dzięki starych procesów technologicznych (8000 – 1500 nm) są częstym obiektem analizy wstecznej dokonywanej przez amatorów i profesjonalistów. W procesorze Z80 jednostka arytmetyczna według specyfikacji jest 8 bitowa jednak jej wykonanie odbywa się dzięki czterech rejestrów w dwustopniowym potoku, patrz Rysunek 3. Pozwoliło to projektantom zaoszczędzić cenne miejsce na chipie a użytkownik / programista nie odczuwa różnicy, gdyż wykonanie programu jest zdefiniowanie przez wydajność innych fragmentów układu i dlatego stopnie potoku są transparentne. Kolejnym problemem jest kompatybilność wsteczna, która często wymusza istnienie artefaktów projektowych tzn. elementów które są umieszczane na chipie ze względu na starsze programy a nie obecny stan techniki. Dobrym przykładem jest proces bootowania (startu) architektury x86 który jest skomplikowany i trudny do zrozumienia dla wielu użytkowników. Na koniec pozostają jeszcze błędy projektowe. Dobrym przykładem jest niewłaściwe zabezpieczenie złączy serwisowych i diagnostycznych. Ich podstawowym celem jest umożliwienie producentowi na wprowadzanie aktualizacji czy odzyskanie danych po awarii jednak niewłaściwie wykonane mogą umożliwić atak bądź zostać oznaczone jako anomalia w budowie. W rezultacie odróżnienie elementów budowy trojana od pozostałych fragmentów układu jest zadaniem bardzo trudnym technicznie wymagającym nie tylko wysokich nakładów finansowych i dobrej infrastruktury, ale co ważniejsze bardzo dużego doświadczenia a często i intuicji.

Pod koniec rewersu informacje uzyskujemy tylko dla konkretnej próbki która na dodatek ulega zniszczeniu. Zatem wciąż nie mamy pewności czy w pozostałych egzemplarzach z partii, z której pobrano badany układ scalony, nie występują zagrożenia. Dlatego w praktyce opisany proces stosuje się dopiero wtedy, gdy są jednoznaczne przesłanki wskazujące na istnienie zagrożenia sprzętowego, bądź gdy chcemy uzyskać tzw. złoty wzorzec. Złoty wzorzec to układ, co do którego mamy pewność, iż nie posiada modyfikacji a zatem analiza może zostać sprowadzona np. do porównania obrazów ze skanowanego chipa z tym właśnie modelem. Podsumowując, inżynieria wsteczna nowoczesnych złożonych kości krzemowych jest żmudnym i podatnym na błędy procesem, na który decydują się głównie klienci instytucjonalni np. duże korporacje bądź instytucje rządowe. Badanie inwazyjne nowszych produktów może wykonać jedynie specjalistyczne laboratorium, które posiada wymagany sprzęt i wykwalifikowany personel.

Metody bezinwazyjne

W rezultacie, zarówno środowisko akademickie jak i przemysł pracują nad nowymi bardziej przystępnymi metodami analizy umożliwiającymi bezinwazyjne wykrywanie zagrożeń sprzętowych, a więc np. sprawdzenie wszystkich egzemplarzy z dużej partii produktów. Wyniki tych prac można w dużym uproszczeniu podzielić na dwie grupy: testy funkcjonalne i analiza informacji z kanałów bocznych. Opiszę je w tej właśnie kolejności.

Testy funkcjonalne to po prostu sformalizowana nazwa popularnego „fuzzingu”. Użytkownik wykorzystuje wszystkie możliwe sygnały wejściowe układu wprowadzając niewłaściwe bądź przypadkowe dane (tzw. wektory wejściowe) i obserwuje sygnały wyjściowe i wyniki pracy (tzw. wektory wyjściowe). Szuka się zatem anomalii i odchyleń (tzw. “dewiacji”) pomiędzy obserwowanymi stanami wyjściowymi a założonymi np. wynikającymi z dokumentacji producenta bądź oczekiwań użytkownika. By takie metody były skuteczne pojawia się konieczność posiadania tzw. złotego wzorca (modelu) czyli dokładnej informacji o tym jak powinien zachować się układ niezainfekowany. Najczęściej w celu stworzenia takiego modelu stosuje się dokumentacje użytkownika a także rewers opisany powyżej. Na pierwszy rzut oka testy funkcjonale wydają się być procesem bardzo zbliżonym do standardowych testów produkcyjnych mających na celu usunięcia ewentualnych wadliwych produktów przed wysłaniem ich do klientów. Niestety większość standardowych testów tego typu nie radzi sobie dobrze z wykrywaniem zagrożeń sprzętowych. Dzieje się tak dlatego iż w przypadku trojanów atakujący stara się ukryć swoje modyfikacje tak by uniknąć przypadkowego wyzwolenia (uruchomienia) układu. Na przykład w przypadku backdoora w procesorze można zastosować skomplikowany wektor wejściowy który analizuje historię stanów jednostki (innymi słowy zależności wynikającej z historii wykonań) co powoduje, iż trzeba przetestować miliony kombinacji. Ponadto trojan sprzętowy wcale nie musi używać wyjść układu komunikując się tzw. kanałami bocznymi. Jego komunikacja może być też ukryta wśród innych danych generowanych przez system (vide techniki obfuskacji) bądź nieuczciwy producent może spreparować dokumentacje i uzyskujemy w rezultacie błędny złoty wzorzec. Czy jest zatem wyjście z sytuacji?

Analiza informacji z tzw. kanałów bocznych

Trojany sprzętowe z definicji to stwarzające niebezpieczeństwo modyfikacje układu których można dokonać na dowolnym etapie produkcji. Każda modyfikacja wpływa w jakimś stopniu na parametry pracy układu i tę zmianę można obserwować np. pobór mocy, opóźnienie w transmisji sygnału, temperatura czy promieniowanie. Na przykład konieczność analizowania (filtrowania) wejść procesora w celu zidentyfikowania kombinacji wyzwalającej niebezpieczny układ prowadzi do dodatkowego opóźnienia w potoku wykonującym instrukcje a także zwiększa zużycie energii. Jednak i w tym wypadku do wykrycia niezbędny jest tzw. „złoty wzorzec” czyli produkt, który na 100% nie zawiera zagrożenia, a więc może być wykorzystany jako punkt odniesienia w pomiarach. Innymi słowy wynik obserwacji jest tak dokładny jak dokładny był nasz model.

Dlatego zwykle te dwie czynności – uzyskanie złotego wzorca i późniejsza analiza w oparciu o ten model – traktuje się jako nierozłączne etapy analizy informacji z kanałów bocznych. Przykładem może być opisany przez Agrawala et al. proces analizy zużycia energii i zmian widma elektro-magentycznego chipu. Pierwszą fazą analizy było wygenerowanie profili poboru energii dla losowej próby z dużej partii układów dostarczonych przez producenta. Ta próba służy następnie do zbudowania modelu, który będzie służył za punkt odniesienia w dalszej analizie. By mieć pewność, iż w tej grupie nie ma układów z zagrożeniami sprzętowymi przechodzą one proces rewersu i dokładanej analizy. W wyniku tych testów partia próbna zostaje zniszczona, ale na postawie uzyskanych danych możliwe jest opracowanie złotego wzorca produktu.

Pozostałe układy z partii mogą być testowane dzięki metod nieinwazyjnych, czyli poprzez zastosowanie tych samych wektorów wejściowych i obserwacje tzw. “profili” poboru mocy w czasie. Następnie dane z profili są analizowane dzięki metod statystycznych w celu odnalezienie anomalii i odchyleń od złotego wzorca, które można już dokładnie przeanalizować.

Jednak i analiza danych z kanałów bocznych nie daje 100% pewności bezpieczeństwa układu, mimo iż zdecydowanie utrudnia zadanie atakującemu. Wraz ze zmniejszającą się wielkością poszczególnych tranzystorów i bramek coraz trudniejsze staje się odróżnienie zmian w pracy układu wynikających z użycia trojana od innych szumów i zakłóceń wynikających np. ze środowiska pracy czyli tzw. tła.

Podsumowanie

Wykrywanie zagrożeń w układach scalonych to trudny proces. Trojany sprzętowe stanowią duże zagrożenie. Ich implementacje są bardzo krótkie (zwiększenie wielkości powierzchni chipa o mniej niż 1%); mogą być łatwo dodane i dobrze zamaskowane, jeżeli projektant jest jednocześnie twórcą konkretniej implementacji bądź ma dostęp do całości dokumentacji.

Wykorzystanie podatności jest proste, a jej odnalezienie bardzo skomplikowane (a w wielu przypadkach praktycznie niemożliwe). Dodatkowo producent może zawsze tłumaczyć „niestandardowe” działanie procesora błędami w konstrukcji (czyli zwykłymi bugami). Dlatego wiele rządów decyduje się na rozwój własnych procesorów, choćby jeżeli możliwości ich rynkowego sukcesu są ograniczone a choćby nieopłacalne ekonomicznie.

Artykuł był opublikowany na zaufanatrzeciastrona.pl .

![[VIDEO] Przez cztery dni robili zakupy obok bomby. Nikt nie wiedział.](https://dzikizachod.eu/wp-content/uploads/2026/04/IMG_7010_compressed_2026_04_10_094123.webp)