To najszybsze w tej chwili pamięci, rozwijane jako kolejne generacje standardu od lat. Teraz dowiadujemy się, jak ów standard będzie osiągał kolejne kamienie milowe w najbliższym czasie.

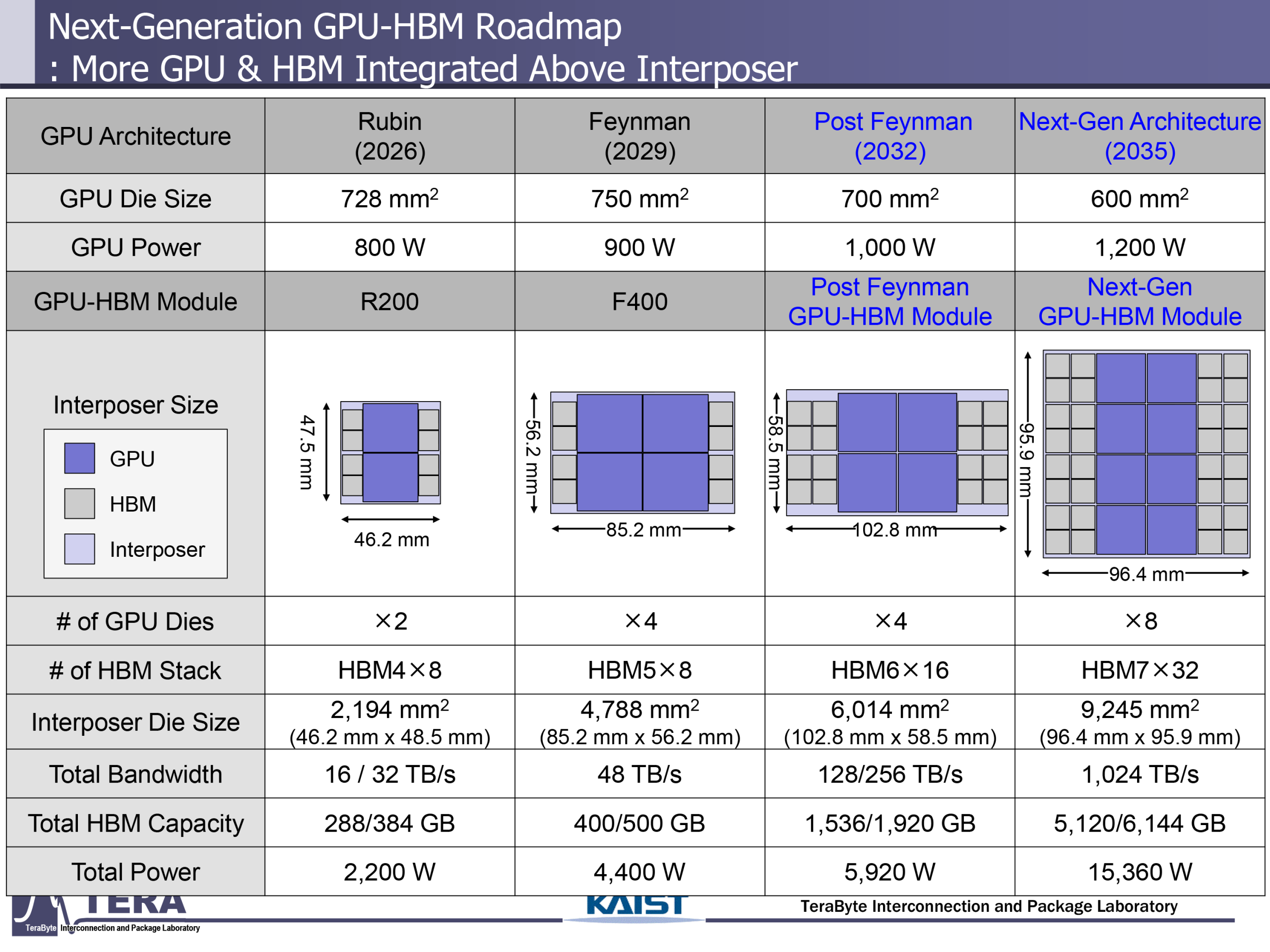

W ciągu najbliższych kilkunastu lat czeka nas prawdziwa rewolucja w dziedzinie pamięci HBM (High Bandwidth Memory). Zgodnie z nową analizą opublikowaną przez Korea Advanced Institute of Science and Technology (KAIST), rozwój tej technologii będzie przebiegać w sposób spektakularny – aż do roku 2038, kiedy to przewidywana jest premiera HBM8. Choć nie są to deklaracje producentów, a akademicka prognoza oparta na obserwacjach rynkowych i rozwoju procesów technologicznych, już dziś daje ona wgląd w to, dokąd zmierza branża pamięci operacyjnych wysokiej przepustowości.

W najbliższych latach spodziewać się można wejścia do produkcji pamięci HBM4, oferującej przepustowość sięgającą 2 TB/s przy interfejsie 2048-bitowym oraz pojemności do choćby 348 GB na stos. To dopiero początek. Około 2029 roku na rynek ma trafić HBM5, z podwojoną przepustowością (4 TB/s) i jeszcze szerszym interfejsem (4096-bit), a także szeregiem nowych funkcji: zintegrowanym cache’em L3, wsparciem dla LPDDR i CXL oraz wbudowanymi czujnikami termicznymi.

HBM6, przewidywane na ok. 2032 rok, to kolejny ogromny skok – do 8 TB/s przy 16 GT/s, pojemności 120 GB i zasilaniu rzędu 120 watów. Technologia ta będzie wykorzystywać bezpośrednie łączenie warstw (direct bonding), hybrydowe mostki silikonowo-szklane oraz zaawansowane wewnętrzne przełączniki. Kluczową rolę odegra także sztuczna inteligencja – nie tylko w projektowaniu struktury układów, ale również w optymalizacji energetycznej i funkcjonowaniu w czasie rzeczywistym.

Punktem kulminacyjnym roadmapy jest jednak HBM8 – planowana na okolice 2038 roku. Przepustowość tej pamięci ma osiągać choćby 64 TB/s, interfejs rozszerzy się do gigantycznych 16 384 bitów, a pobór mocy wzrośnie do około 180 W. Pojawi się również fundamentalna innowacja: integracja pamięci NAND wewnątrz stosu HBM, co umożliwi przesyłanie danych bezpośrednio pomiędzy warstwami, z pominięciem CPU czy GPU. Tego typu rozwiązanie otwiera drogę do zupełnie nowej klasy układów – pamięci hybrydowych łączących szybkość RAM i pojemność NAND w jednym ekosystemie, z pełną trójwymiarową architekturą oraz zaawansowanymi metodami chłodzenia.

Wnioski z roadmapy KAIST są jasne: HBM nie tylko pozostanie kluczowym elementem infrastruktury AI i HPC, ale ewoluuje w kierunku jeszcze większej przepustowości, gęstości i funkcjonalności. To także sygnał dla branży: przygotujmy się na czasy, w których pojedynczy stos pamięci będzie zużywał więcej energii niż cały procesor, ale jednocześnie dostarczał dane z prędkością kilkudziesięciu terabajtów na sekundę.